Solution Overview

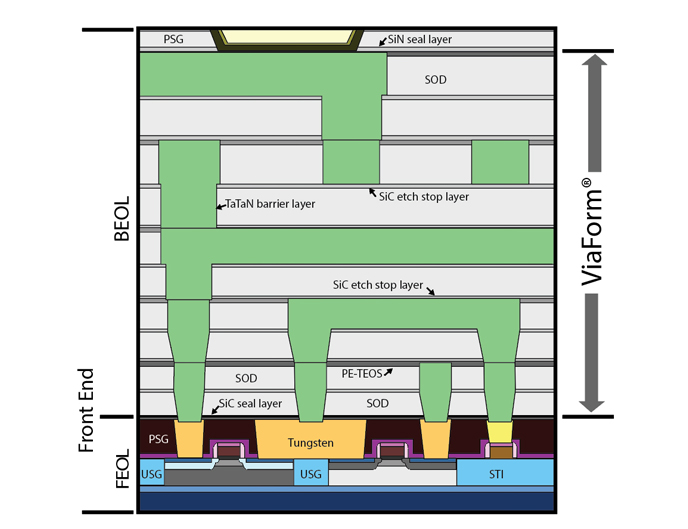

The sequence to fabricate Cu interconnects is called the “dual-damascene” process. Nanoscale vias and trenches are first etched in a dielectric layer (typically SiO2) followed by deposition of diffusion barrier layer(s). A thin Cu seed layer is then sputtered, followed by Cu electroplating to form complex nanopatterns. Finally, excess Cu plated in the field regions is removed by CMP. The multilayered interconnect network may consist of 7–10 interconnect levels.

ViaForm® products, most widely used in dual-damascene process world-wide, ensure the bottom-up copper electroplating to achieve void-free metallization of complex nano patterns.